Microelectronics package overview and technical requirements

In recent years, various electronic products have been widely used in industry, agriculture, national defense, and daily life. With the rapid development of electronic science and technology, the rapid development of the microelectronics industry is largely due to the rapid development of microelectronics packaging technology. Today, the world is ushering in the era of electronic information technology with electronic computers as its core. With its development, electronic products are increasingly required to have high performance, versatility, high reliability, miniaturization, thinness, convenience, and popularity. Popularization of the required low-grade features. This will inevitably require microelectronics packaging to be better, lighter, thinner, higher packing density, better electrical and thermal performance, higher reliability, and higher cost performance.

First, the outline of microelectronics package

1, the concept of microelectronic packaging

Microelectronics packaging refers to the use of membrane technology and micro-fabrication technology, the chip and other elements in the frame or substrate layout, paste and fix and connect, lead out the connection terminals and through a plastic insulating dielectric potting and fixing, to form the overall three-dimensional structure of the process. In a broader sense, it refers to the process of connecting and fixing a package and a substrate, assembling a complete system or electronic device, and determining the overall performance of the entire system.

2, the purpose of microelectronic packaging

The purpose of the microelectronic package is to protect the chip from or be affected by the external environment and provide a good working condition for the circuit to have stable and normal functions.

3. Technical Field of Microelectronics Packaging

Microelectronics encapsulation technology covers a wide area of ​​technology and is a complex system engineering. It involves various disciplines such as physics, chemistry, chemical engineering, materials, machinery, electrical and automation, and also uses various materials such as metals, ceramics, glass, polymers, etc. Therefore, microelectronics packaging is an interdisciplinary integration of knowledge. Science, integrating the product's electrical characteristics, heat transfer characteristics, reliability, application of materials and process technology, and cost and other factors, in order to achieve the optimization of the engineering technology.

In the pursuit of upgrading the functions and levels of microelectronics products, the importance of developing new packaging technologies is no less important than circuit design and process technology. The electronic industries in all countries in the world are all making efforts to research and development in order to obtain a leading position in this field.

4, the function of microelectronic packaging

There are four main functions implemented by the microelectronic package:

Power transmission mainly refers to the distribution and conduction of the power voltage.

The transmitted circuit signal is mainly to reduce the delay of the electrical signal as much as possible. During the wiring, the signal and the interconnect path of the chip should be as short as possible and the path elicited through the encapsulated I/O interface should be the shortest.

Providing a heat dissipation method mainly means that various packages must consider the problem of how to dissipate the accumulated heat when the components and components work for a long time.

Structural protection and support, mainly refers to the package can provide solid and reliable mechanical support for connecting parts, and can adapt to changes in various working environments and conditions.

5, the technical level of microelectronic packaging

Microelectronic packages usually have four levels:

The first level refers to the process of pasting and fixing the circuit chip and the package substrate or the lead frame, circuit connection and package protection, so as to make it easy to take and transport, and can be connected to the next level of assembly module element.

The second level: the process of combining several first-level packages and other electronic components into one circuit card.

Third level: The process of combining several circuit cards assembled in the second level into a single circuit board to make it a component or subsystem.

Level 4: Assemble several subsystems into one process for completing electronic products.

The wiring process between the circuit components on the chip is also referred to as a zero-level package, so the package engineering can also be differentiated in five levels.

6. Classification of Microelectronic Packages

According to the number of combinatorial circuit chips in the package, microelectronic packages can be classified into single chip packages (SCP) and multichip packages (MCP). MCP refers to lower level multichip packages, while MCM refers to higher levels. Chip package.

According to the sealed material, it can be divided into polymer-based (ie, plastic) and ceramic-based categories. The ceramic package has stable thermal properties, excellent thermal conductivity, and good barrier to water molecules penetration. Therefore, it is the main high-reliability packaging method. The plastic package has the advantages of process automation, low-cost, thin package, etc. Therefore, the plastic package is The most commonly used technology in the market today.

According to the device and circuit board interconnection, the package can be divided into two types: pin insertion type (PTH) and surface mount type (SMT). The pins of the PTH device are fine needle-like or thin plate-like metals, which are inserted into the guide hole of the base or the circuit board for soldering and fixing; the SMT device is first attached to the circuit board and then fixed by welding. It has a gull-wing type and hook. Type, straight shank-type metal pins, or electrode bump pins (also called unleaded devices).

According to the pin distribution pattern, there are four kinds of package components: single-side pins, bilateral pins, four-sided pins, and bottom pins. The common unilateral pins are single-in-line (SIP) and cross-pin type (ZIP); bilateral pin components are dual-inline packages (DIP), miniaturized packages (SOP), etc.; four-sided pins have four sides Flat package (QFP), bottom pin with metal can (MCP) and point array package (PGA).

Due to the miniaturization of products and the advancements in function and process technology, there are many different variations in the form and internal structure of packaging.

7, microelectronics packaging materials

The materials used in microelectronic packaging include metals, ceramics, glass, and polymers. The metal is mainly an electrically conductive material. Ceramics and glass are the main components of a ceramic package substrate. Glass is also an important sealing material. The plastic package uses a polymer resin. Sealing components and housings, polymer materials are also important additives in many packaging processes. The use and choice of materials are related to the requirements of the electrothermal properties, reliability, technology and process, and cost of the package.

Second, the technical requirements of microelectronic packaging

With the rapid development of the microelectronics industry, microelectronics packaging technology has also continued to develop and progress.

1, miniaturization

Microelectronics packaging technology has evolved in the direction of miniaturization and has emerged as an ultra-compact package with the same size as the chip, namely wafer-level packaging technology (WLP). The low cost, high quality, short delivery time, and external dimensions conforming to international standards are all necessary conditions for miniaturization.

2, adapt to high fever

Since the thermal resistance of the microelectronic package is increased due to the reduction in size, the use environment of the electronic device is complicated, and therefore the heat dissipation of the package must be solved. Especially under high temperature conditions, the stability and reliability of long-term operation must be guaranteed.

3, high density

As the integration of components becomes higher and higher, more and more pins are required for microelectronic packages, and the spacing between pins is getting smaller and smaller.

4, adapt to multiple pins

More and more external leads are a major feature of microelectronics packages. Of course, they are also difficult because pin spacing cannot be infinitely small, and solder can not be stably supplied during reflow soldering. The failure rate is high.

The multi-pin package is the mainstream in the future, so the technical requirements of microelectronic packaging should be adapted to multiple pins as much as possible.

Third, the development status of microelectronics packaging in China

In the past, the entire semiconductor industry in China was very weak, but package testing with relatively low added value was the strongest link in the entire semiconductor industry chain and accounted for more than 59% of the domestic semiconductor industry value. This is because in the semiconductor industry chain, package testing has low capital requirements and technical barriers, and the manpower demand is relatively high, while domestic companies have abundant and low labor resources. However, this is still at a level comparable to the international advanced packaging and testing technologies. gap.

According to relevant reports, in 2003, China's microelectronics packaging and testing companies realized sales revenue of 24.6 billion yuan, an increase of 23.3% year-on-year, accounting for 70% of the entire microelectronics industry chain sales revenue, which has become a new bright spot in the rapid development of the microelectronics industry. The rapid increase in production capacity has met the requirements of the market, and has also led to an increase in output, such as Changjiang Electronics (600584, shares), Nantong Fujitsu, Sichuan Ansommei, China Resources Ansheng, Shanghai Jinpeng, Anju, Zhejiang Huayue, etc. The company has achieved historical success in production sales revenue profits.

From the survey data analysis, domestic microelectronics packaging is in a rapid development stage. Various joint-stock companies, Sino-foreign joint ventures, wholly foreign-owned enterprises, and private enterprises have sprung up. Its main set

In the Yangtze River Delta, China is followed by the Pearl River Delta and the Bohai Sea region of Beijing-Tianjin. However, according to the data from the China Semiconductor Industry Association, there are about 210 companies engaged in discrete device and microelectronics packaging testing at the present stage, among which there are more than 100 manufacturers engaged in microelectronics packaging, but they actually have a certain level of packaging and testing technology, and There are less than 20 companies with annual packaging capacity of more than 100 million units. It is expected that if Taiwan-funded enterprises can smoothly remove regulatory restrictions and increase production capacity in the next three years, there will be fierce killing elimination matches or mergers and acquisitions in the country.

The domestic microelectronics packaging and testing industry can be subdivided into three phases.

Prior to 1995, the vast majority of domestic packaging and testing were dependent on local component manufacturers, such as Shanghai Advanced, Belling, Wuxi Huajing, and Shougang NEC, and some of them were joint ventures or other forms of cooperation with foreign companies such as Shenzhen Saiyi Microelectronics and modern electronics (now acquired by Jinpeng), but the investment scope is mainly based on PDIP, PQFP, and TSOP.

However, since 1995, the first professional package foundry (Aftek) has appeared in the country, followed by the integration of international giants such as Intel, AMD, Samsung Electronics, and Motorola as a result of national policy support for the development of the IC industry. Component manufacturers have expanded their investments and have entered China with more than US$100 million in investment.

After 2000, wafer foundries such as SMIC, Grace, Hejian, and Taiwan Semiconductor Manufacturing Co., Ltd. were established one after another. With the opening of new production capacity and the continuous expansion of production capacity, the demand for the later-stage packaging production capacity became more urgent, making the professional sealing and measuring plants the Competition for orders, but also with the landing continued to station around the wafer factory, such as Wei Yu Technology, Hua Hong NEC to provide BGA/CSP and other high-end packaging services, SMIC and Jin Peng established mutual exclusion alliance.

As wafer manufacturing began to advance to higher-order technologies, the requirements for the packaging process began to shift to higher-order products, which will also lead to further improvement in the quality of China's domestic packaging and testing industry.

IV. Key Technologies of Microelectronics Packaging

The development of microelectronics packaging technology aims to make the system work toward miniaturization, high performance, high reliability and low cost. From the perspective of technological development, the key technologies for microelectronics packaging are: TCP, BGA, FCT, CSP , MCM and 3D packaging.

1, with a load package

A tape carrier package (TCP) is a package in which an LSI bare chip is mounted on a tape-shaped insulating tape forming a connection wiring and connected to a lead wire. Compared with the QFP, the lead pitch of the TCP can be made narrower, and the shape can be made thinner. Therefore, the TCP is a high-density package that is thinner than the QFP, and it occupies a small area on the PCB board and can be used for High I/O counts for ASICs and microprocessors.

2. Gate array package

A gate array package (BGA) is a type of surface mount package. On the back of a printed circuit board, a two-dimensional array is arranged with ball pads instead of lead pins. The LSE chip is mounted on the front side of a printed circuit board, and it is sealed by injection molding and potting resin, and it can be used for a multi-pin LSI package with more than 200 pins. The package size is also smaller than QFP. And BGA is not like QFP, do not worry about the deformation of the lead.

3, flip chip technology

Flip chip technology (FCT) is to face the substrate with the active area of ​​the chip, and realize the interconnection between the chip and the substrate through the solder bumps arranged in an array on the chip. This method can provide higher I/O density. Its main advantages are: the shape is reduced in size. Improve electrical performance. High I/O density. Good heat dissipation. Improve fatigue life and improve reliability. Bare chip testability.

4, chip scale package

Chip Scale Packages (CSPs) mainly include pin-less CSPs for memory devices and multi-pin CSPs for ASCIs, specifically chip-on-chip (LOC), miniature ball grid array (MBA), and surface array (LGA). . Its main advantages are: easy measurement and aging, easy installation and easy reflow soldering.

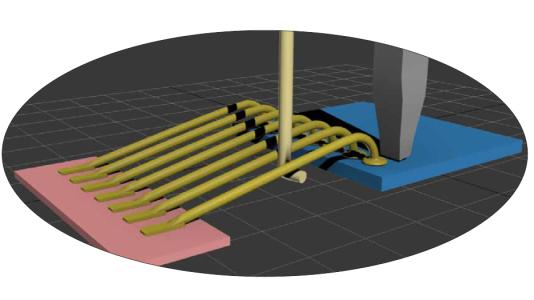

5, multi-chip mode

The multi-chip mode (MCM) means that a plurality of semiconductor bare chips are surface mounted on the same wiring board. According to different substrate materials, it is divided into three categories: MCM-L, MCM-C, and MCM-D.

MCM-L refers to a mode in which a multilayer printed circuit board is made of normal glass or epoxy resin. The wiring density is high and the price is low.

MCM-C uses a thick film technology to form a multi-layer wiring ceramic, which is used as a substrate. The wiring density is higher than MCM-L.

MCM-D forms multi-layer wiring ceramics through thin-film technology or directly uses Si and Al as substrates, with the highest wiring density and high price.

6, three-dimensional (3D) package

Three-dimensional packaging is the increase in the density of microelectronics assembled into space. Not only does it use higher packing density, it also has more features, higher transmission speeds, lower power consumption, and better performance and reliability.

Fifth, the development trend of microelectronics packaging

In the 21st century, the concept of microelectronic packaging has changed from traditional device-oriented to system-oriented, which further expands on the basis of traditional functions such as packaged signal transmission, support carrier, heat conduction, and chip protection, and utilizes thin film, thick film technology, and embedded technology. The system's signal transmission circuit and most of the active and passive components are integrated and combined with the chip's high-density packaging and component-attachment processes to achieve system-wide package integration to achieve the highest density package.

In the near future, BGA technology will continue to advance with the fastest growth speed as the mainstream technology of the package with its advantages in performance and price; CSP technology has very good prospects, and will be widely used in fast memory as its cost is gradually reduced. , logic circuits and ASICs are encapsulated in various products; in the future, FCT technology will be used as a basic mainstream packaging technology to infiltrate a variety of different package forms; with the market of portable electronic devices. Rapidly expanding, MCM is suitable for high-speed, high-performance development speed is quite amazing; three-dimensional packaging is the best development of the packaging technology, with the further development of its technology, it will become the most widely used packaging technology.

In summary, from the perspective of device development, the development trend of the packaging technology in the future is: the development of single chip to multi-chip; the development of planar package to three-dimensional package; and the development of independent chip package to system integration package.

Shenzhen Innovative Cloud Computer Co., Ltd. , https://www.xcypc.com