Teach you how to eliminate the factors that affect the JESD204B link transmission

The JESD204B serial data link interface was developed to support the growing bandwidth requirements of higher speed converters. As a third-generation standard, it offers a higher channel rate maximum (up to 12.5 Gbps per channel), supporting the determination of delay and harmonic frame clocks. In addition, thanks to the improved performance of the converters - these converters are compatible with open market FPGA solutions and scalable - it is now easy to transfer large amounts of data to be processed.

FPGA vendors have been discussing the topic of Gigabit Serial/Deserialization (SERDES) interfaces for many years, although most analog-to-digital converters (ADCs) and digital-to-analog converters (DACs) have not been equipped with such high-speed serials in the past. interface. FPGAs and converters do not interface with any common standard and cannot take advantage of the high bandwidth of SERDES. The JESD204B-compatible converter solves this problem, and people have raised some questions about this new feature.

What is 8b/10b encoding, why is this encoding required for the JESD204B interface?

There is no guarantee that the DC balanced signal on the differential channel will not be disturbed by random uncoded serial data, as it is likely that a large amount of opposite 1 or 0 data will be transmitted. Random data transmitted over a serial link may also be inactive for long periods of time and be all 1s or all 0s for a relatively long period of time.

When this happens, the DC balance of the unencoded serial data stream is isolated, resulting in one of two extreme cases. At this time, if valid data is transmitted again on the link, a bit error is likely to occur because the line starts to be biased again. In addition, a long-term problem is electron migration because the other side of the differential pair will maintain a differential DC voltage on one side. To overcome these problems, the 8b/10b encoding scheme is typically employed in differential serial data streams, including JESD204B.

The 8b/10b code uses 10 data bits to send 8-bit initial information from the source transmitter through a look-up table. This approach has an inherent cost of 25% (10b/8b = 1.25) and is less efficient. In addition, encoding allows for the transmission of at least 3 bits (but no more than 8 bits) of data per 10-bit symbol. This ensures that the receiver has enough conversion data to recover the embedded clock information regardless of the dynamic activity of the underlying data.

When using 8b/10b encoding, the deviation between binary 0 and 1 in the serial data stream is kept within ±1, so the signal remains DC balanced for a long time. Then, 10-bit to 8-bit reverse decoding must be performed on the data stream at the receiver side to recover the original data using the reverse lookup table. The more efficient 64b/66b encoding works similarly, but with an overhead of only 3.125%. This approach is more advanced and may be used in future releases of JESD204.

The JESD204B channel I assigned to the converter could not be routed to the FPGA on the system board. There are too many crossovers and it is very susceptible to crosstalk. Can I remap the channel assignment of JESD204B to improve the layout?

Although the converter's JESD204B serial channel may specify its specific link-specific relationship by numbers, letters, or other terms, this relationship does not have to be fixed. The specification allows remapping of assignment relationships in the initial configuration data as long as each channel and device has a unique identification number. The link configuration data contains the device and channel identification number to identify its operation. Using this information, the multi-channel transmitter can easily redistribute any digital logic serial data to any physical output channel through a crossbar multiplexer.

Although this is an optional feature of the specification license, if the ADC vendor provides a crossbar multiplexer function that redistributes the logic output to the physical output, the link I/O can be reconfigured to the optimal order. Provides maximum convenience for place and route. The FPGA receiver can receive the same initial configuration data and change the expected channel assignment to recover the data. With this feature, channel routing from one device to another is much simpler and can be independent of the initial name assigned by the silicon vendor in the data sheet.

I am trying to design a converter using JESD204B multipoint link in my system. How is it different from a single point link?

The JESD204B specification provides an interface called a "multipoint link." It is a communication link that connects three or more JESD204B devices. Depending on how the converter is used, this link configuration is more efficient in some cases than a single point link.

For example, a two-channel ADC using JESD204B. In most cases, a dual ADC provides a single clock input for two converters. It will force the ADC to perform analog sampling at the same frequency. However, for some specific applications, these devices may also use two independent input clocks, each of which can drive the corresponding ADC separately. Thus, there is a possibility of sampling phase difference between the two ADCs, even each The ADCs are individually sampled at mutually unrelated frequencies. In the latter case, there is data from all two converters on a single JESD204B link, and it does not work without a complex back-end FIFO scheme.

One solution to this problem is to have a dual-channel converter using a multipoint link JESD204B interface, each of which uses its own separate serial link output. Non-coherent clocks can then be used for each ADC, and the output of each serial link can be easily routed separately to a separate FPGA or ASIC. Multi-drop configuration can also be used to stream multiple streams of a single FPGA To multiple DACs. As the number of devices on the link increases, minimizing the clock skew of the device in a multipoint configuration can be a very challenging task.

What is the determined delay in JESD204B? Is it the total delay of the converter?

The total delay of the ADC represents the time it takes to input an analog sample, process, and output a digital signal from the device. Similarly, the total delay of the DAC represents the time from the digital sample data input device to the analog output of the corresponding sample. Typically, both are measured at resolution for the sample clock period because they are frequency dependent. This is in principle different from the definition of the determined delay described in the JESD204B link deployment.

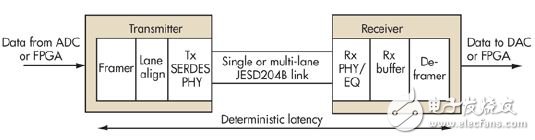

The determined delay of the JESD204B link is defined as the time it takes for data to propagate from the parallel frame data input of the transmitter (ADC or source FPGA) to the parallel deframed data output of the receiver (DAC or receiver FPGA). This time is typically measured in resolution for the frame clock period or at the device clock (Figure 1). This definition does not include the analog front end core of the ADC or the back end analog core of the DAC. Not only are the two devices used as a function in this delay calculation, but serial data signal routing with the two devices is also used as a function to participate in the calculation. This means that the delay is determined to be greater or less than the determined delay in a multi-converter system or multi-drop link, depending on the routing length of the JESD204B channel. The receiver's buffer delay helps to compensate for the delay differences caused by routing.

Figure 1. Concept of JESD204B determining the delay between the frame wrapper and the framer of two interconnected devices. The example delay function consists of three terms: the transmitter, the receiver, and the interface propagation time between them.

How does JESD204B use the end bit? What is the meaning of the end position?

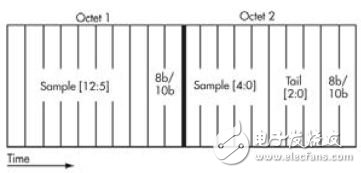

The JESD204B link allows more than the actual required information space to be used to transmit converter data and control bits. If the data for a particular converter or configuration does not fill the entire space, it is filled with the end bit in the definition. For example, the space of N'=16 is larger than the 13-bit actual data after packing (N = 13 + CS = 0). In this case, the unused data space will be filled with 3 end bits (Figure 2).

Figure 2. If the converter uses only 13-bit sample data, then 3 end bits can be used to complement the second 8-bit word of N'=16.

The end bit is a dummy data bit with no information content and is only used to completely fill unused space. If the end bits are filled with repeated static values, they may produce interference spurious noise; but they can also be used to represent pseudo-random sequences. Both the transmitter and the receiver must understand that these bits contain no information based on the link configuration so that the receiver can easily remove them from the associated data stream.

There is no problem with my link mode, but the transmitter does not send data in normal operating mode. In modern converters, the low voltage differential signaling (LVDS) and parallel interface allow simple detection/debugging of the least significant bit (LSB) or most significant bit (MSB) of the DAC or ADC to check if the function converter is operating. How to detect MSB or LSB when using JESD204B interface?

This is one of the few drawbacks of the JESD204B interface. It is not easy to electrically detect the LSB or MSB I/O to see if there is correct activity on the link in both directions of the converter. This is because the sampled data is serialized in units of channels, so it is not easy to electrically detect specific weighted data bits. However, if you want to quickly see if the converter is sending or receiving any valid data (if it does exist), there are still some ways to do so.

Some oscilloscope vendors provide real-time data processing to serially decode 8b/10b data and display unencoded data streams on the oscilloscope screen. In this way, unscrambled data can be detected to determine what activity is taking place on the link.

FPGA vendors provide an internal probing software tool that connects to a computer via a USB dongle, giving system designers a way to view I/O data sent and received within the FPGA. In addition, some ASICs and converters provide an internal serial loopback self-test mode that can be used to identify data problems on the link.

Assuming that other link parameters are known, how do you calculate the channel rate of the converter?

If other key parameters of the converter, ASIC, or FPGA are known, the system designer using JESD204B can easily calculate the number of channels or channel rates for the link. All basic link parameters have a mathematical relationship as shown below, from which unknown variables can be calculated. Based on the calculations, the system designer can select other parameters within the converter or FPGA-defined architecture to change the link operation.

Channel rate = (M &TImes; N'&TImes; [10/8] &TImes; Fs) / L

Where M is the number of on-link converters, N' is the number of information bits in a single sample (including sample resolution, control, and end bits), Fs is the device or sample clock, L is the number of channels, and channel rate is represented. The bit rate of a single channel, 10/8 represents the link overhead of 8b/10b encoding.

For example, consider the case of a two-channel ADC: N'= 16, Fs = 235 MHz uses two channels. What is the channel rate?

Channel rate = [2 &TImes; 16 × 1.25 × 235 MHz] / 2

Channel rate = 4700 Mbps or 4.7 Gbps

What is the application layer and what can it do?

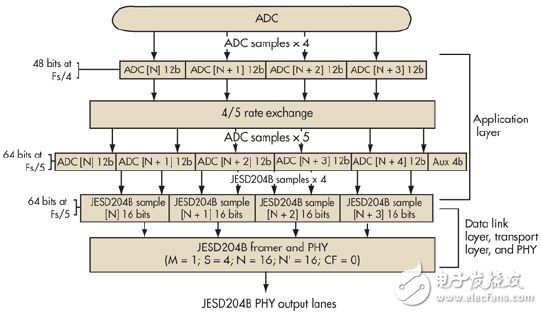

The application layer is a method provided by JESD204B that allows sample data to be mapped outside of normal specifications. This is very useful for some converter modes that need to transmit a data sample size different from link N'.

Using the application layer, you can make the inefficient configuration of the original channel with a lower number of channels or a smaller channel rate more efficient. Both the transmitter and the receiver need to be configured to understand the specific application layer, as the specific converter mode can be customized or targeted to the application layer. Figure 3 shows an example where 5 samples are allocated to a space that is typically only occupied by 4 samples.

When applying the layer calculation using the equation in the previous question, you need to use the valid N' instead of the actual N'. For example, in the application layer example shown below, although the actual JESD024B sample N' parameter is 16, the valid N' of the ADC sample can be calculated because in this example, 5 samples are transmitted with 64 bits. Therefore, Neff = 64/5 = 12.8. Since the other variables remain the same, the channel rate will drop by 20%:

Neff/N' = 12.8 / 16 = 0.8.

Figure 3. The ADC application layer can remap five 12-bit ADC samples to four JESD204B. N'= 16 samples. 4 additional auxiliary information can be used for other purposes.

What is the outlook?

As JESD204B continues to grow in the data converter market, the FPGA platform's ability to protect intellectual property (IP) will drive this trend. Although this technology is more complicated, future discussions on this topic will continue as more engineers begin to use JESD204B to design new systems.

Copper Lugs,Copper Cable Lugs,Plating Copper Cable Lugs,Copper Tube Terminal Lugs

Taixing Longyi Terminals Co.,Ltd. , https://www.txlyterminals.com