Unexpanded clock reveals

Clock expansion is a big challenge for engineers using the Xilinx Vivado Design Suite, but it is not an insurmountable obstacle.

As more and more Xilinx users start using the Vivado® design suite, some users are confused about the unexpanded clock. So what is an unexpanded clock? How do they relate and time? What is the standard way to deal with unexpanded clocks? Let's take a closer look at this issue, with a focus on ways to ensure that designers use the correct synchronization techniques to safely traverse the clock domain crossing between unexpanded clocks.

With the introduction of the Vivado tool, Xilinx is now able to support timing constraints in the industry-standard Synopsys Design Constraint (SDC) format. This is a major shift in the way the ISE Design Suite tools handle timing. The fundamental difference between the Vivado suites is that all clocks are associated with each other by default. Thus, the unconstrained timing path in ISE is constrained in the Vivado Design Suite. If there is no periodic relationship between the two clocks, this constraint can result in very tight timing requirements.

An unexpanded clock is a clock that does not have a periodic relationship with another clock in 1,000 clock cycles. The Vivado BFT core paradigm is a good way to show how unexpanded clocks work.

The originating and capturing timing paths begin with an initiating event and are terminated by a capture event. The initiating event occurs when the clock of the synchronization unit transitions from the non-working state to the working state. The capture event occurs when the clock of the downstream or the synchronization unit responsible for the capture transitions from the inactive state to the active state. The time required between the initiation of an event and the capture of an event is referred to as a "path requirement," which represents the time between the occurrence of valid data after the event has been initiated and at the capture unit pin.

If the initiating clock and the acquisition clock are both in the same physical clock network, the path requirement refers only to the clock period. Taking the 250MHz clock as an example, if the working edge of the initiating unit and the capturing unit are the same (rising edge vs. rising edge or falling edge pair falling edge), the time interval between the initiating event and the capturing event is exactly 4 nanoseconds. If the working edge of the initiating unit and the capturing unit are different, the path must be time-calculated at half the clock frequency. This is the case where the rising edge of the clock is switched to the falling edge or the falling edge to the rising edge. For a 250 MHz clock, the corresponding path requirement is 2 nanoseconds.

In the case where the source clock and the desTInaTIon clock are not the same clock, the timing problem becomes more complicated. Timing paths with different clock sources and clock targets are referred to as cross-clock domain (CDC) paths.

If the phase relationship between the originating clock and the capture clock is unknown, the path requirements cannot be calculated. Due to the uncertain phase relationship, the path timing cannot be accurately determined. Unsafe clocks are highlighted in the clock interaction report generated by the Vivado Design Suite. In the case where the phase relationship between the initiating clock and the capturing clock is known, the path requirement can be mathematically derived as long as there is a periodic relationship between the two clocks. The method used to determine the minimum path requirement between a given initiating clock and the acquisition clock is called clock stretching. However, determining whether there is a periodic relationship between the two clocks needs to be constrained by the actual limit, because in general there is no common periodic feature between the two different clocks.

The practical limit used by the Vivado Design Suite is 1,000 clock cycles, which is measured by the smaller of the two clocks. If there is no periodic relationship after extending two clocks to more than 1,000 clock cycles, then these two clocks are called "unexpanded" clocks.

The path between the two unexpanded clocks required by the Vivado Design Suite is the minimum time between the originating clock and the adjacent working edge of the capture clock. However, it is important to note that there are more stringent path requirements for more than 1,000 clock cycles, which is why the Vivado Design Suite calls the relationship between the two clocks of this type unexpanded.

The Vivado BFT core provides the ideal setting for testing different clock rates to determine if two clocks are extended clocks

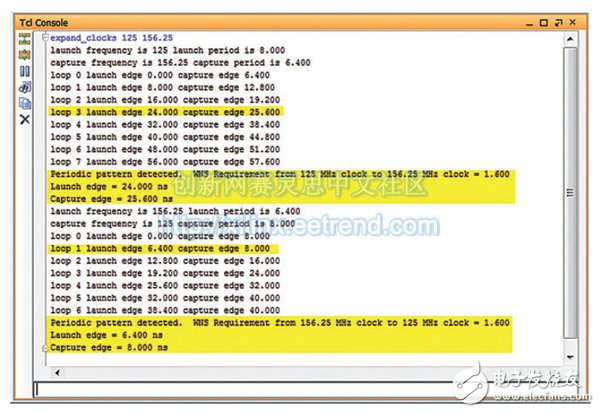

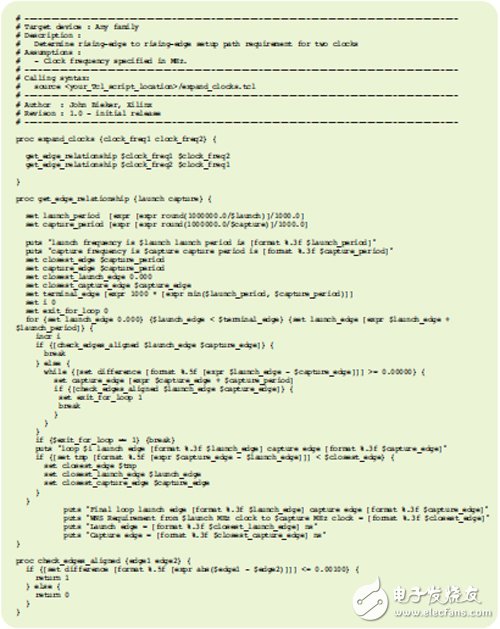

To better understand how the Vivado Design Suite calculates unexpanded clocks, the TCL script in Figure 1 is used to detail the method of extending the rising edge to the rising edge path between any two clock rates. Figure 2 shows the output of this script, an extension of two clocks running at 125MHz and 156.25MHz respectively.

Figure 1 - Extended Clock TCL Script

Figure 2 - Clock Expansion for 125MHz and 156.25MHz Clocks

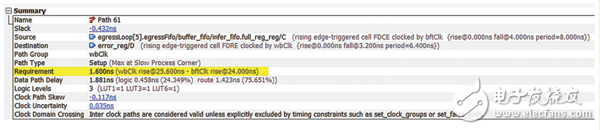

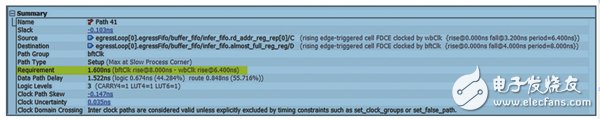

To confirm the results of the above TCL script, let's take a look at the Vivado BFT kernel example design. The BFT core provides an ideal setting for testing different clock rates to determine if two clocks are extended clocks. The core has two separate clock sources, named wbClk and bftClk. Timing constraints set the frequencies of wbClk and bftClk to 100MHz and 200MHz, respectively. The user can modify such constraints on any two clock rates to determine the extended relationship as determined by the Vivado timing engine. Figure 3 shows the results displayed when bftClk is set to 125MHz and wbClk is set to 156.25MHz, and the associated timing is provided (report_TIming –from [get_clocks bftClk] -to [get_clocks wbClk]). Note that the prediction results of the TCL script are confirmed by the initiator edge, capture edge, and timing requirements.

Figure 3 - Clock Expansion from 125MHz Start Clock to 156.25MHz Capture Clock

Table 1 is the initiator edge, capture edge, and path requirements for several clock rates obtained using the TCL script in Figure 4.

Figure 4 - Clock Extension Tcl Script

Handling Unexpanded Clocks People often treat unexpanded clocks as asynchronous clocks and process them through appropriate synchronization techniques such as FIFOs, edge detectors, or synchronizer circuits. If the user uses such techniques, timing exceptions should be used in the constraint to handle unexpanded clocks (typically using set_false_path or set_max_delay exceptions).

Understanding and explaining the unexpanded clock is important because the edge relationship between the clocks will determine the path requirements used by the timing engine in the Vivado Design Suite. Xilinx wants to scrutinize all of the unexpanded clocks in the design to ensure that the cross-clock domain between unexpanded clocks is safely traversed using appropriate synchronization techniques.

Silicone Glass Fiber Tube,Pre Insulated Tube,Braided Shield Sleeve,Wire Shielding Sleeve

Shenzhen Huiyunhai Tech.Co., Ltd. , https://www.cablesleevefactory.com