The underlying embedded functional unit and soft core, hard core and solid core

The embedded function module mainly refers to a soft processing core (Soft Core) such as a DLL (Delay Locked Loop), a PLL (Phase Locked Loop), or a DSP. Nowadays, more and more embedded functional units make the single-chip FPGA a system-level design tool, which has the ability to jointly design software and hardware, and gradually transition to the SOC platform.

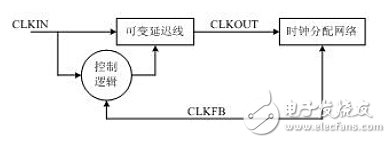

The DLL and PLL have similar functions for clock precision and low jitter multiplier and crossover, as well as duty cycle adjustment and shift equalization. Xilinx's chips integrate DCM and DLL, Altera's chips integrate PLLs, and LatTIce's new chips integrate PLLs and DLLs. PLLs and DLLs can be easily managed and configured with tools generated by IP cores. The structure of the DLL is shown in Figure 2-8.

The embedded dedicated hard core is relative to the underlying embedded soft core. It refers to the hard core (Hard Core) with powerful FPGA processing, which is equivalent to the ASIC circuit. To improve FPGA performance, chip manufacturers have integrated specialized hard cores inside the chip. For example, in order to increase the multiplication speed of FPGAs, dedicated multipliers are integrated in mainstream FPGAs. In order to apply communication bus and interface standards, many high-end FPGAs integrate serial-to-parallel transceivers (SERDES), which can reach tens of Gbps. Transceiver speed.

Xilinx's high-end products not only integrate Power PC series CPUs, but also embedded DSP Core modules. The corresponding system-level design tools are EDK and Platform Studio, and the concept of System on Chip is proposed accordingly. . Through the platforms such as PowerPC?, Miroblaze, and Picoblaze, it is possible to develop standard DSP processors and related applications to achieve the development goals of SOC.

In addition, the new Xilinx FPGA family, such as the Virtex-5 LXT, also has built-in PCI Express and tri-state Ethernet MAC hard core (TEMAC). Compared with the soft core implementation, the hard core can reduce the power consumption by 5~. 10 times, saving nearly 90% of the logical resources.

The Xilinx Tri-Mode Ethernet MAC core is a parameterizable core that is ideal for use in network equipment such as switches and routers. The customizable TEMAC core enables system designers to implement a wide range of integrated Ethernet designs, from low-cost 10/100 Ethernet to higher-performance 1GB ports. The TEMAC core design is compliant with the IEEE 802.3 specification and can operate in 1000Mbps, 100 Mbps, and 10 Mbps modes.

In addition, it supports half-duplex and full-duplex operation. The TEMAC core is available through the Xilinx CORE GeneratorTM tool and is part of the Xilinx full suite of Ethernet solutions.

2.1.3 Concept of soft core, hard core and solid core IP (Intelligent Property) Core is a general term for integrated circuit cores with intellectual property cores. It is a repeatedly verified macro module with specific functions. It can be transplanted to different semiconductor processes regardless of the chip manufacturing process. By the SOC stage, IP core design has become an important task for ASIC circuit design companies and FPGA providers, as well as their strength. For FPGA development software, the richer the IP cores provided, the more convenient the user's design will be, and the higher the market occupancy rate. Currently, IP cores have become the basic unit of system design and are exchanged, transferred and sold as independent design results.

From the way IP cores are provided, they are usually divided into three categories: soft core, solid core and hard core. The hard core cost is the largest in terms of the cost of completing the IP core; in terms of flexibility of use, the soft core has the highest reusability.

The soft core in the EDA design field refers to the previous register transfer level (RTL) model; specifically in the FPGA design refers to the hardware language description of the circuit, including logic description, netlist and help documentation. The soft core is only functionally simulated and needs to be integrated and laid out to be used. The advantages are high flexibility and portability, allowing users to self-configure; the disadvantage is that the predictability of the module is low, there is the possibility of error in the subsequent design, and there is a certain design risk. Soft cores are the most widely used form of IP cores.

2. Solid IP CoreIn the EDA design field, the solid core refers to the netlist with plane planning information; in the FPGA design, it can be regarded as a soft core with layout planning, usually provided in a mixed form of RTL code and corresponding specific process netlist. The RTL description is combined with a specific standard cell library for comprehensive optimization design to form a gate-level netlist, which can then be used by the place-and-route tool. Compared with the soft core, the design flexibility of the solid core is slightly worse, but the reliability is greatly improved. At present, solid core is also one of the mainstream forms of IP core.

3. Hard IP CoreHard cores refer to proven design layouts in the EDA design landscape; specifically in FPGA design, designs that are fixed in layout and process, verified through front-end and back-end, cannot be modified by designers. There are two reasons why it cannot be modified: first, the system design has strict timing requirements for each module, and it is not allowed to disturb the existing physical layout; secondly, the requirements for protecting intellectual property rights are not allowed to be changed by the designer. The impractical modification of the IP hard core makes it difficult to reuse, so it can only be used in certain applications and has a narrow range of applications.

Litecoin is an online currency based on peer-to-peer technology and is an open source software project under the MIT/X11 license. It can help users make instant payments to anyone in the world [2]. Litecoin was designed and programmed by a programmer (Li Qiwei) who used to work at Google, and launched on January 9, 2011. Litecoin is an improved digital currency inspired by Bitcoin. The technical principle of Litecoin is the same as that of Bitcoin. It also adopts a decentralized architecture, without any central authority control, and the issuance of new coins and the transfer of transactions and payments are based on open source encryption algorithms, etc. These are all imitated the design principle of Bitcoin. However, Litecoin tries its best to improve the shortcomings that Bitcoin has shown before, such as too slow transaction confirmation, small total cap, the emergence of large mining pools caused by proof-of-work mechanism and so on, SHA256 algorithm [1].

Litecoin, which aims to improve Bitcoin, has three significant differences. First, the Litecoin network can process a block every 2.5 minutes instead of 10, thus providing faster transaction confirmation. Second, the Litecoin network is expected to produce 84 million litecoins, four times the amount of money issued on the Bitcoin network. Each litecoin is divided into 100 million smaller units, defined by eight decimal places.

Litecoin Mining Machine:Bitmain Antminer L7,Goldshell Mini-DOGE Pro,Goldshell LT Lite,Innosilicon A4+ LTCMaster,Goldshell LT5,

Bitmain Antminer L3+ (504Mh),Bitmain Antminer L3+ (600Mh),etc.

Litecoin Mining Machine,L3 Miner,Antminer L7,Ltc Mining Machine,Scrypt

Shenzhen YLHM Technology Co., Ltd. , https://www.apgelectrical.com